# Agilent N4850A DigRF v3 Acquisition Probe N4860A DigRF v3 Stimulus Probe

Data Sheet

# Evaluate and integrate your DigRF v3 components more easily

#### **DigRF v3 Challenges**

The DigRF v3 standard presents new challenges for mobile wireless development, integration and validation teams as the communications link between the BB-ICs and the RF-ICs evolve from analog to digital. Digital IQ data and control information are transferred between the BB-IC and the RF-IC over the DigRF v3 interface. Engineers traditionally use spectrum analyzers to evaluate the analog interface between the BB-IC and the RF-IC, but now they need new tools because spectrum analyzers are incapable of measuring the DigRF v3 digital serial interface.

RF-IC development teams must verify operation of the RF-IC before the start of the handset integration phase. Spectrum analyzers and signal sources are no longer sufficient for characterizing the new generation of RF-ICs that comply to the DigRF v3 standard. To validate RF-IC operation, engineering teams need DigRF v3 digital serial stimulus and analysis tools that operate in concert with the traditional RF tools.

The challenges for BB-IC validation teams mirrors that of the RF-IC teams, as the signal sources and spectrum analyzers must be replaced by DigRF v3 digital serial stimulus and analysis tools to validate BB-IC functionality.

#### Meeting the DigRF v3 Challenges

The Agilent Technologies N4850A acquisition probe and the N4860A stimulus probe operate in conjunction with Agilent 16800 and 16900 Series serial logic analyzers to provide the digital serial stimulus and acquisition capabilities required to independently evaluate an RF-IC or BB-IC with a DigRF v3 interface or integrate your mobile wireless designs.

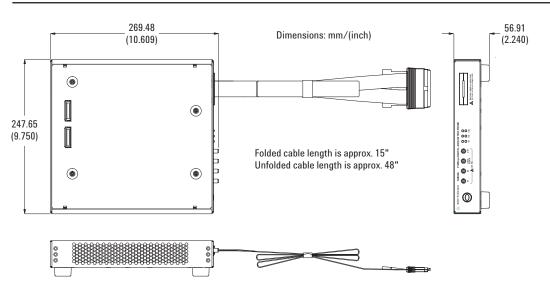

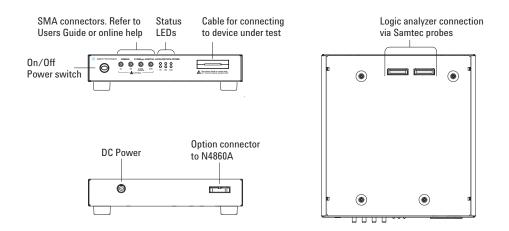

Figure 1. N4850A DigRF v3 acquistion probe

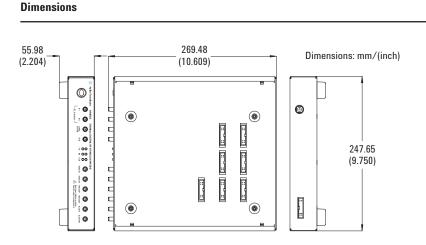

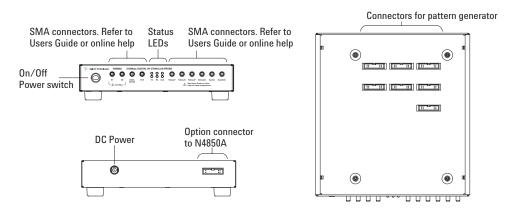

Figure 2. N4860A DigRF v3 stimulus probe

### Introduction to DigRF v3

The DigRF v3 standard was designed to enable interoperability between RF-ICs and BB-ICs from different suppliers. Additional benefits include reduced cost, higher bandwidth and extended battery life.

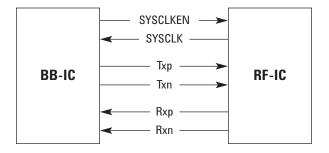

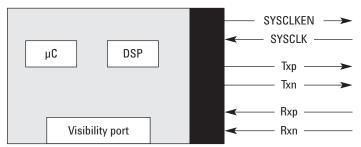

The physical layer of the DigRF v3 interface consists of six signals (see Figure 3) with independent transmit and receive paths. Additional signals are specified for diversity mode. The DigRF v3 specification allows for 1.8 V LVDS, 1.2 V LVDS or SLVDS electrical interface voltages. The DigRF v3 interface transitions between high speed, low power and sleep modes dynamically.

The DigRF v3 standard specifies data packets and control packets. Embedded in the data packets is the digital IQ representation of the RF signal. Control packets contain the configuration and status information necessary to keep the BB-IC and RF-IC operating in synchronization.

Figure 3. DigRF v3 physical interconnect scheme

### **Test Scenarios**

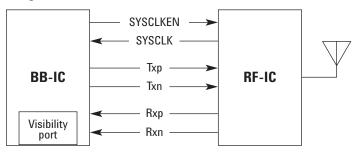

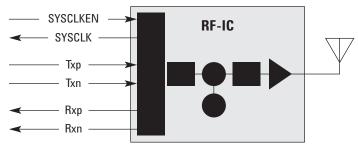

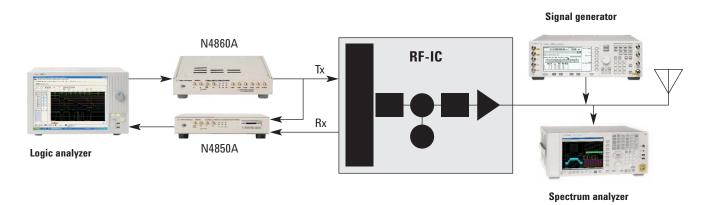

RF-IC development teams, BB-IC development teams and integration teams each have unique test and measurement requirements as they validate their products, as shown in Figures 4a-4c.

#### Integration measurement needs

- Acquire Tx and Rx transactions

- Decode/view control packets

- Extract digital IQ (Rx and Tx) for vector signal analysis

- Monitor BB-IC internal operations

#### Figure 4a. The integration team's measurement needs

#### **RF-IC evaluation measurement needs**

- Generate and drive control packets

- Generate and drive digital IQ (Tx)

- Acquire digital IQ (Rx) for vector signal analysis

Figure 4b. Measurement needs for evaluating the RF-IC

#### **BB-IC** evaluation measurement needs

- Decode and view control packets (Tx)

- Extract digital IQ (Tx) for vector signal analysis

- Generate and drive digital IQ (Rx)

- Monitor BB-IC internal operations

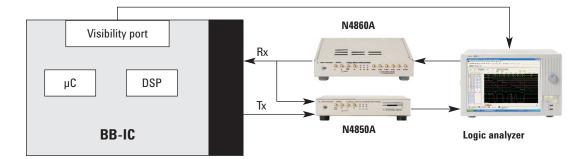

#### Figure 4c. Measurement needs for evaluating the BB-IC

### **BB-IC/RF-IC Integration**

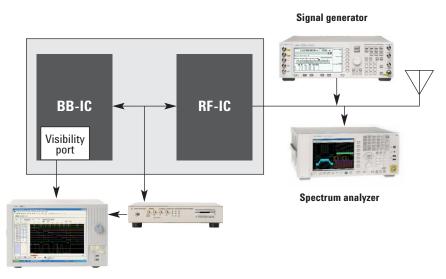

Figure 5 shows the equipment required to integrate the RF-IC with the BB-IC. A signal generator and spectrum analyzer provide stimulus/response capabilities in the RF domain. Traffic on the DigRF v3 link between the RF-IC and BB-IC is monitored by the N4850A acquisition probe. Control packets are viewed in the logic analyzer's packet viewer, and IQ data packets are analyzed using the Agilent 89601A vector signal analysis package. The logic analyzer monitors the BB-IC visibility port to help you gain insight into µC and DSP and correlate these internal operations with traffic on the DigRF v3 interface.

Visibility into the internal operation of the BB-IC can be achieved by monitoring the visibility port, which is designed into the BB-IC. Typically, you can track operation of the microcontroller and DSP through the visibility port. This allows you to analyze control flow, track internal processing of digital IQ and correlate BB-IC internal operations to DigRF v3 traffic.

Logic analyzer

| Edit View Setup Iools                                                                   |                            |                          |                                                   | 1.0       | 10 KT 1.4    | en lite lite  | -       |  |

|-----------------------------------------------------------------------------------------|----------------------------|--------------------------|---------------------------------------------------|-----------|--------------|---------------|---------|--|

| © 2 3 4 5 1 1 1 2 2 1 1 2 2 3 5 1 4 7 7<br>■ 2 2 - 11 2 2 2 3 5 1 4 7 7 2 5 5 1 4 7 7 7 |                            |                          |                                                   |           |              |               |         |  |

| Sample Number                                                                           | ARM11 ETM Inverse Assembly |                          | Number ARM11 ETM Inverse Assembly Address TRACEDA |           | TRACEDATA    | TA Cycle Type |         |  |

| 12.6                                                                                    | AND                        | R0,R1,#0x00000002 Exec   | ER RO+54                                          |           | Instruction  | Other         | 0       |  |

| 12.7                                                                                    | CMP                        | R0, #0x00000002 Exec     | ER RO+58                                          |           | Instruction  |               |         |  |

| 12.8                                                                                    | BLEO                       | 0x00008050 Exec          | ER RO+5C                                          |           |              | Conditional   | Branc   |  |

| 12.9                                                                                    | MRC                        | p14,1,R1,c0,c4,0 Exec    | ER RO+50                                          |           |              | Coprocessor   |         |  |

| 12.10                                                                                   | AND                        | R0, R1, #0x00000002 Exec | ER RO+54                                          |           | Instruction  |               |         |  |

| 12.11                                                                                   | CMP                        | R0, #0x00000002 Exec     | ER RO+58                                          |           | Instruction  |               |         |  |

| 12.12                                                                                   | BLEO                       | 0x00008050 Exec          | ER RO+5C                                          |           |              | Conditional   | Branc   |  |

| 12.13                                                                                   | MRC                        | p14,1,R1,c0,c4,0 Exec    | ER RO+50                                          |           |              | Coprocessor   | Diadire |  |

| 12.14                                                                                   | AND                        | R0,R1,#0x00000002 Exec   | ER RO+54                                          |           | Instruction  |               |         |  |

| 12.15                                                                                   | CMP                        | R0,#0x00000002 Exec      | ER RO+58                                          |           | Instruction  |               |         |  |

| 12.16                                                                                   | BLEO                       | 0x00008050 Exec          | ER RO+5C                                          |           |              | Conditional   | Branc   |  |

| 13                                                                                      |                            |                          |                                                   | 0000 66BC | ETM Raw Dat  | a             |         |  |

|                                                                                         | Etm Phead                  | ier(Format1)             |                                                   |           | ETM Other P  |               |         |  |

| 13.2                                                                                    | MRC                        | p14,1,R1,c0,c4,0 Exec    | ER RO+50                                          |           |              | Coprocessor   |         |  |

| 13.3                                                                                    | AND                        | R0.R1.#0x00000002 Exec   | ER RO+54                                          |           | Instruction  |               |         |  |

| 13.4                                                                                    | CMP                        | R0.#0x00000002 Exec      | ER RO+58                                          |           | Instruction  |               |         |  |

| 13.5                                                                                    | BLEO                       | 0x00008050 Exec          | ER RO+5C                                          |           | Instruction  | Conditional   | Branc   |  |

| 13.6                                                                                    | MRC                        | p14,1,R1,c0,c4,0 Exec    | ER RO+50                                          |           | Instruction  | Coprocessor   |         |  |

| 13.7                                                                                    | AND                        | R0,R1,#0x00000002 Exec   | ER RO+54                                          |           | Instruction  |               |         |  |

| 13.8                                                                                    | CMP                        | R0, #0x00000002 Exec     | ER RO+58                                          |           | Instruction  | Other         |         |  |

| 13.9                                                                                    | BLEO                       | 0x00008050 Exec          | ER RO+5C                                          |           | Instruction  | Conditional   | Branc   |  |

| 13.10                                                                                   | MRC                        | p14,1,R1,c0,c4,0 Exec    | ER RO+50                                          |           |              | Coprocessor   |         |  |

| 13.11                                                                                   | AND                        | R0, R1, #0x00000002 Exec | ER RO+54                                          |           | Instruction  |               |         |  |

| 13,12                                                                                   | CMP                        | R0, #0x00000002 Exec     | ER RO+58                                          |           | Instruction  | Other         |         |  |

| 13.13                                                                                   | BLEO                       | 0x00008050 Exec          | ER RO+5C                                          |           |              | Conditional   | Branc   |  |

| 13.14                                                                                   | MRC                        | p14,1,R1,c0,c4,0 Exec    | ER RO+50                                          |           |              | Coprocessor   |         |  |

| 13.15                                                                                   | AND                        | R0,R1,#0x00000002 Exec   | ER RO+54                                          |           | Instruction  |               |         |  |

| 13.16                                                                                   | CMP                        | R0,#0x00000002 Exec      | ER RO+58                                          |           | Instruction  |               |         |  |

| 14                                                                                      |                            |                          |                                                   | 0000 66BC | ETM Raw Dat  | a             |         |  |

| 14.1                                                                                    | Etm Phead                  | ier(Format1)             |                                                   |           | ETM Other P  |               |         |  |

| 14.2                                                                                    | BLEQ                       | 0x00008050 Exec          | ER RO+5C                                          |           | Instruction  | Conditional   | Branc   |  |

| 14.3                                                                                    | MRC                        | p14,1,R1,c0,c4,0 Exec    | ER RO+50                                          |           |              | Coprocessor   |         |  |

| 14.4                                                                                    | AND                        | R0,R1,#0x00000002 Exec   | ER RO+54                                          |           | Instruction  |               |         |  |

| 14.5                                                                                    | CMP                        | R0, #0x00000002 Exec     | ER RO+58                                          |           | Instruction  | Other         |         |  |

| 14.6                                                                                    | BLEQ                       | 0x00008050 Exec          | ER RO+5C                                          |           | Instruction  | Conditional   | Branc   |  |

| 11.7                                                                                    | MDC                        |                          | ED DOLLEO                                         |           | Treatmention | C             |         |  |

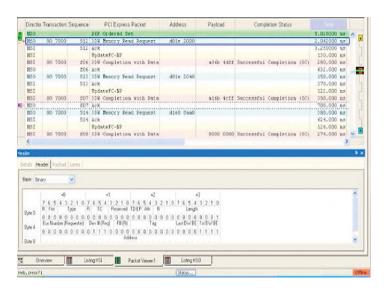

Figure 6. Decoder view of BB-IC internal operation

### **BB-IC/RF-IC Integration** (continued)

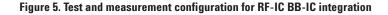

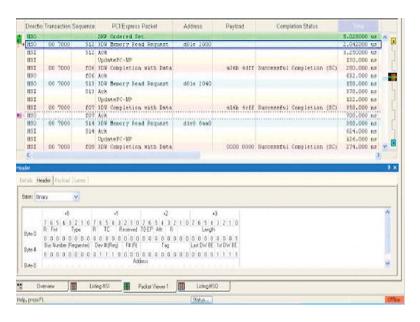

The N4850A acquisition probe captures transactions on the Tx and Rx paths of the DigRF v3 interface independently. Control packets are decoded and displayed on the logic analyzer's packet viewer as illustrated in Figure 7. These capabilities enable you to track the status and control flow of the system under test to identify defects and tune performance parameters.

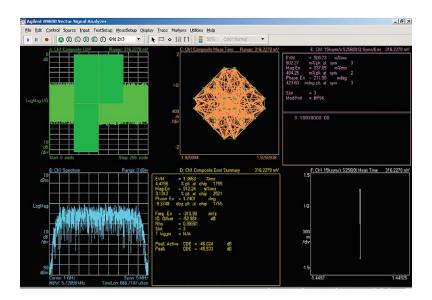

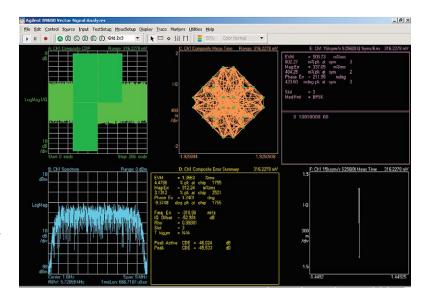

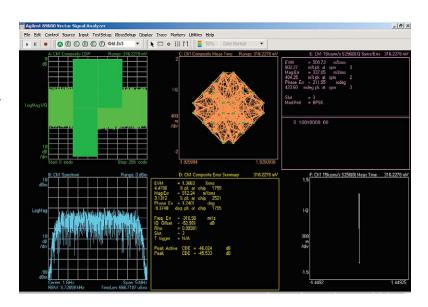

There is a two-step process for analyzing the digital IQ data packets that are acquired by the N4850A acquisition probe. Using the signal extractor tool, the headers and padding are removed, leaving the digital IQ representation of the RF signal. The IQ data then can be analyzed by the vector signal analysis package to evaluate EMV, sidebands and other critical RF parameters. This capability enables systems integrators to characterize RF-IC behavior and adjust DSP algorithms or the **RF-IC** configuration to optimize performance.

Figure 7. Packet view of DigRF v3 control traffic

Figure 8. Vector signal analysis of DigRF v3 digital IQ

### **RF-IC Evaluation**

Figure 9 shows a test and measurement configuration that will enable RF-IC designers to verify operation of their components with the DigRF v3 interface. Stimulus and analysis of the RF interface is provided by a signal generator and a spectrum analyzer. Serial digital acquisition and stimulus for the DigRF v3 interface are provided by the N4850A and N4860A operating under control of an Agilent 16800 or 16900 Series logic analyzer. With the ability to monitor and control the RF-IC through the DigRF v3 interface, validation engineers can evaluate transmitter and receiver behavior.

Figure 9. Test equipment configuration to verify RF-IC operation

### **RF-IC Evaluation** (continued)

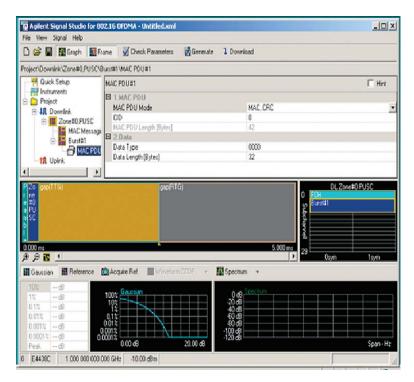

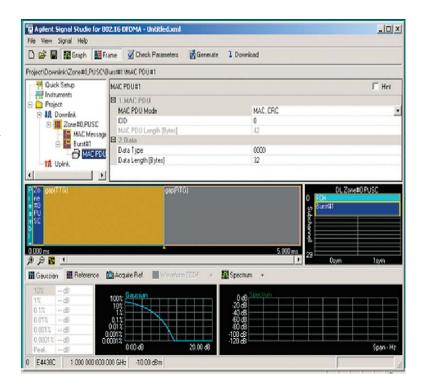

The logic analyzer enables you to specify the desired RF-IC configuration. The specified configuration is embedded into DigRF v3 control packets. The N4860A stimulus probe outputs DigRF v3-compliant control packets that configure the RF-IC.

Digital IQ data can be loaded into the logic analyzer from a variety of sources, including Signal Studio and Advanced Design System (ADS). The logic analyzer embeds the IQ data in DigRF v3-compliant packets. The data packets are transferred to the RF-IC with the proper timing by the stimulus probe. The RF-IC processes the digital IQ data and generates an RF signal, which is characterized using a spectrum analyzer. Control packets, as specified by the user, can be inserted into the data packet flow while looping through the waveform. With this feature, you can make RF-IC configuration adjustments - like the gain setting of the RF amplifiers - interactively.

| <b>H</b> | 1                  |              |              |         |       |      |       | Edit | 8   |

|----------|--------------------|--------------|--------------|---------|-------|------|-------|------|-----|

|          | Instruction Vector | DATA         | TIME         | NSYSCLK | FRAME | SIZE | SLEEP | TABS | TSE |

| Line #   | Instruction vector | Hex          | Hex          | Hex     | Hex   | Hex  | Hex   | Hex  | He  |

| 0        | Init Start         |              |              |         |       |      |       |      |     |

| 1        | Init End           |              |              |         |       |      |       |      |     |

| 2        | Nain Start         |              |              |         |       |      |       |      |     |

| 3        | Comment            | RESET        |              |         |       |      |       |      |     |

| 4        | Vector             | 00 0000      | 0000         | 1       | 0     | 0    | 0     | 0    |     |

| 5        | Comment            | SET ABSOLUT  | E TIMER TO 0 |         |       |      |       |      | (   |

| 6        | Vector             | 00 0000      | 0000         | 1       | 0     | 0    | 0     | 1    |     |

| 7        | Comment            | WAIT 3NS     |              |         |       |      |       |      |     |

| 8        | Vector             | 00 0003      | TTTT         | 0       | 0     | C    | 0     | 1    |     |

| 9        | Comment 5          | SET ABSOLUTI | E TIMER TO 0 | AGAN    |       |      |       |      |     |

| 10       | Vector             | 00 000       | 0000         | 0       | 0     | C    | 0     | 1    |     |

| 11       | Comment            | PACKET       |              |         |       |      |       |      |     |

| 12       | Vector             | OG EFOD      | 0000         | 0       | 1     | 3    | 0     | 0    |     |

| 13       | Comment            | PACKET       |              |         |       |      |       |      |     |

| 14       | Vector             | 00 3800      | 0000         | 0       | 1     | 3    | 0     | G    |     |

| 15       | Comment            | WAIT ABSOLU  |              |         |       |      |       |      |     |

| 16       | Vector             | 00 0001      | 0120         | 0       | 0     | C    | 0     | 1    |     |

| 17       | Comment            | PACKET       |              |         |       |      |       |      |     |

| 18       | Vector             | 00 3200      | 0000         | 0       | 1     | 3    | 0     | 0    |     |

| 19       | Nain End           |              |              |         |       |      |       |      |     |

Figure 11. Generation of digital IQ representation of RF signal

### **RF-IC Evaluation** (continued)

Using the logic analyzer and stimulus probe, the RF-IC can be configured to receive an RF signal. The RF signal source generates the RF waveform of interest. The RF-IC processes the waveform and generates a DigRF v3 serial bit stream with the resulting digital IQ data. The acquisition probe captures the DigRF v3 data packets generated by the RF-IC and extracts the digital IQ data for analysis using the vector signal analysis package.

Figure 12. Vector signal analysis of digital IQ on the logic analyzer

### **BB-IC Evaluation**

Figure 13 shows the test and measurement configuration that will enable BB-IC designers to verify operation of their components with the DigRF v3 interface. Visibility into the internal operation of the BB-IC is acquired by the logic analyzer through the BB-IC visibility port. The acquisition probe enables the logic analyzer to monitor traffic on the DigRF v3 Tx path as generated by the BB-IC. The stimulus probe can be configured to generate control and digital IQ data packets for the BB-IC over the DigRF v3 Rx path. Validation engineers can use these capabilities to evaluate many of the critical blocks within the BB-IC. Visibility into the internal operation of the BB-IC can be achieved by monitoring the visibility port, which is designed into the BB-IC. Typically, you can track microcontroller and DSP operation through the visibility port. In this manner, control flow can be analyzed and internal processing of digital IQ can be tracked.

Figure 13. Test equipment configuration needed to verify BB-IC operation

|     | E 🛛 🕹 🗚 🦌 🗚      | ATRIAS     | 4. (* )                   |          | 112       | ***                       | / 7. |

|-----|------------------|------------|---------------------------|----------|-----------|---------------------------|------|

|     | Sample Number    | A          | RM11 ETM Inverse Assembly | Address  | TRACEDATA | Cycle Type                |      |

|     | 12.6             | AND        | R0,R1,#0x00000002 Exec    | ER RO+54 |           | Instruction Other         |      |

|     | 12.7             | CMP        | R0,#0x00000002 Exec       | ER RO+58 |           | Instruction Other         |      |

|     | 12.8             | BLEQ       | 0x00008050 Exec           | ER RO+5C |           | Instruction Conditional   | Brai |

|     | 12.9             | MRC        | p14,1,R1,c0,c4,0 Exec     | ER RO+50 |           | Instruction Coprocessor   |      |

|     | 12.10            | AND        | R0,R1,#0x00000002 Exec    | ER RO+54 |           | Instruction Other         |      |

|     | 12.11            | CMP        | R0.#0x00000002 Exec       | ER RO+58 |           | Instruction Other         |      |

|     | 12.12            | BLEO       | 0x00008050 Exec           | ER RO+5C |           | Instruction Conditional   | Bra  |

|     | 12.13            | MRC        | p14,1,R1,c0,c4,0 Exec     | ER RO+50 |           | Instruction Coprocessor   |      |

|     | 12.14            | AND        | R0, R1, #0x00000002 Exec  | ER RO+54 |           | Instruction Other         |      |

|     | 12.15            | CMP        | R0.#0x00000002 Exec       | ER RO+58 |           | Instruction Other         |      |

|     | 12.16            | BLEO       | 0x00008050 Exec           | ER RO+5C |           | Instruction Conditional   | Bra  |

|     | 13               |            |                           |          | 0000 66BC | ETM Raw Data              |      |

|     | 13.1 1           | Etm Pheade | er(Format1)               |          |           | ETM Other Packet          |      |

|     | 13.2             | MRC        | p14,1,R1,c0,c4,0 Exec     | ER RO+50 |           | Instruction Coprocessor   |      |

|     | 13.3             | AND        | R0, R1, #0x00000002 Exec  | ER RO+54 |           | Instruction Other         |      |

|     | 13.4             | CMP        | R0.#0x00000002 Exec       | ER RO+58 |           | Instruction Other         |      |

|     | 13.5             | BLEO       | 0x00008050 Exec           | ER RO+5C |           | Instruction Conditional   | Bra  |

|     | 13.6             | MRC        | p14,1,R1,c0,c4,0 Exec     | ER RO+50 |           | Instruction Coprocessor   |      |

|     | 13.7             | AND        | R0,R1,#0x00000002 Exec    | ER RO+54 |           | Instruction Other         |      |

|     | 13.8             | CMP        | R0, #0x00000002 Exec      | ER RO+58 |           | Instruction Other         |      |

|     | 13.9             | BLEQ       | 0x00008050 Exec           | ER RO+5C |           | Instruction Conditional   | Bra  |

|     | 13.10            | MRC        | p14.1.R1.c0.c4.0 Exec     | ER RO+50 |           | Instruction Coprocessor   |      |

|     | 13.11            | AND        | R0, R1, #0x00000002 Exec  | ER RO+54 |           | Instruction Other         |      |

|     | 13.12            | CMP        | R0, #0x00000002 Exec      | ER RO+58 |           | Instruction Other         |      |

|     | 13.13            | BLEQ       | 0x00008050 Exec           | ER RO+5C |           | Instruction Conditional   | Bra  |

|     | 13.14            | MRC        | p14,1,R1,c0,c4,0 Exec     | ER RO+50 |           | Instruction Coprocessor   |      |

| 4+  | Shadp/15         | AND        | R0, R1, #0x00000002 Exec  | ER RO+54 |           | Instruction Other         |      |

| ale | Shee <b>t</b> 4U | .¢mm       | R0,#0x00000002 Exec       | ER RO+58 |           | Instruction Other         |      |

|     | 14               |            |                           | _        | 0000 66BC | ETM Raw Data              |      |

|     | 14.1 1           | Etm Pheade | er(Format1)               |          |           | ETM Other Packet          |      |

|     | 14.2             | BLEQ       | 0x00008050 Exec           | ER_RO+5C |           | Instruction Conditional   | Bra  |

|     | 14.3             | MRC        | p14,1,R1,c0,c4,0 Exec     | ER RO+50 |           | Instruction Coprocessor   |      |

|     | 14.4             | AND        | R0, R1, #0x00000002 Exec  | ER RO+54 |           | Instruction Other         |      |

|     | 14.5             | CMP        | R0, #0x00000002 Exec      | ER RO+58 |           | Instruction Other         |      |

| 12  | 14.6             | BLEQ       | 0x00008050 Exec           | ER RO+5C |           | Instruction Conditional   | Bra  |

| *   | <                | Vine       |                           | ED DOLEO |           | Testisand in Conservation | -    |

Figure 14. Decoder view of BB-IC internal operation

#### **BB-IC Evaluation** (continued)

The N4850A acquisition probe captures the Tx traffic generated by the BB-IC. The control packets are identified by the logic analyzer, decoded and displayed on the logic analyzer using the packet viewer. Debug and validation of the configuration and control functions of the BB-IC/RF-IC interface are accelerated by using these capabilities.

The N4850A acquisition probe captures the Tx traffic generated by the BB-IC. The data packets are identified and the digital IQ data is extracted from these packets using the signal extractor tool. The digital IQ data is analyzed by the 89601A vector signal analysis tools running on the logic analyzer. These capabilities enable BB-IC validation team to validate that the digital IQ was properly converted to DigRF v3 format. In addition, the DSP algorithms that generated the IQ can be evaluated.

Figure 15. Protocol decode view of DigRF v3 control traffic

Figure 16. Vector signal analysis of DigRF v3 digital IQ

### **BB-IC Evaluation** (continued)

Digital IQ data and control signals are formatted into DigRF v3-compliant packets on the logic analyzer. The N4860A stimulates the BB-IC with the specified data and control packets. In this manner, BB-IC validation teams can analyze how the BB-IC handles the breadth of status and control responses that an RF-IC could generate and how the BB-IC handles various digital IQ streams.

Figure 17. Generation of digital IQ representation of RF signals using Signal Studio

# Characteristics for N4850A DigRF v3 Digital Acquisition Probe

| Features                                                                                                                                               | Benefits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Supports state analysis of DigRF v3<br>standard; 2.5G and 3GPP air<br>standards – e.g. GSM, EDGE, CDMA,<br>CDMA-2K, W-CDMA                             | Validate and troubleshoot handsets and mobile wireless devices incorporating DigRF v3 across a wide variety of over-air standards                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Maximum acquisition speed: 312 Mbps                                                                                                                    | Run at any DigRF v3-compliant operating mode (sleep, low, medium, high speed) with performance headroom                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Supports Voltage Level compliant with standard                                                                                                         | Acquire traffic, no matter which DigRF v3-compliant voltage level you are using.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| SysClk speed support: 19.2 MHz,<br>26.0 MHz, 38.4 MHz                                                                                                  | Acquire traffic, no matter which DigRF v3-compliant speed you are using                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Tracks changes in speed modes                                                                                                                          | Verify mode change algorithms real time with a single acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Acquire 17 differential channels                                                                                                                       | Simultaneously monitor a Tx/Rx bidirectional bus, even with Tx and Rx running at different bus modes                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Converts serial bus stream to parallel format                                                                                                          | Parallel format enables you to trigger on protocol-specific packets, specific bits within a packet (for example, control bits within a packet), and protocol violations – getting you to the root cause of a problem quicker. In addition, combine the parallel format with a logic analyzer that has deep acquisition memory to capture even more system activity, in both directions, for analysis and debug.                                                                                                               |  |  |  |  |  |

| DigRF v3 protocol decoder and packet viewer                                                                                                            | Quickly analyze and debug DigRF v3 digital control and raw IQ data in an intuitive format.<br>The packet viewer lets you operate at the packet level or view detailed information for each<br>individual packet.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| LEDs: Two each for Tx, Rx, and CLK<br>Tx: Speed and synchronization status<br>Rx: Speed and synchronization status<br>CLK: SysClk is enabled, disabled | Quickly identify the status of your system by just looking at the probe. DigRF v3 error detection<br>includes:<br>Tx/Rx<br>• Detected data speed does not match requested speed<br>• Unable to locate stable data; excessive jitter impacts data eye closure<br>• Too little time between SysClk toggling to data toggling (time definition is user defined)<br>Clock<br>• Clock stopped in the middle of a frame<br>• SysClk toggling when SysClkEN is false<br>• Start-of-frame sync not found even though data is toggling |  |  |  |  |  |

| Select the specific Tx/Rx signals, control, and data information to be captured by the logic analyzer                                                  | Focus only on the data you want to see                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

# Characteristics for N4850A DigRF v3 Digital Acquisition Probe (continued)

| Features                                                                                                                                                                        | Benefits                                                                                                                                                                            |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Extract and transfer digital IQ<br>generated from your over-air data to<br>89600 VSA software                                                                                   | Rapidly work through scenarios that let you identify RF signal problems quickly and fine tune your DSP algorithm                                                                    |  |  |  |  |

| Connection port to N4860A digital stimulus probe                                                                                                                                | Perform comprehensive stimulus and acquisition testing                                                                                                                              |  |  |  |  |

| ldentifies invalid sync words so you<br>can trigger on them with an external<br>device, like an oscilloscope                                                                    | Quickly identify faults in order to perform functional and parametric analysis around the fault condition                                                                           |  |  |  |  |

| Supports up to 2048 bits for<br>user-defined payload                                                                                                                            | The tools provide support for your custom data packets                                                                                                                              |  |  |  |  |

| Stack or rack multiple N4850A<br>acquisition or N4860A stimulus probes                                                                                                          | The small probe minimizes the footprint of test equipment next to the device under test                                                                                             |  |  |  |  |

| Configuration files                                                                                                                                                             | Saves time and simplifies measurement setup                                                                                                                                         |  |  |  |  |

| Probe the device under test with<br>a variety of differential probes:<br>E5381A flying leads, E5387A or<br>5495A soft touch connectorless<br>probes, or the E5379A Samtec probe | The high-bandwidth E5381A differential flying leads provide the highest signal-quality measurement. In addition, probing flexibility allows you to use soft touch or Samtec probes. |  |  |  |  |

| Correlate DigRF v3 activity with microcontroller and DSP operation                                                                                                              | A correlated system view enables you to rapidly isolate defects and verify system operation                                                                                         |  |  |  |  |

# **Characteristics for N4860A 312-Mbps Digital Stimulus Probe**

| Features                                                                                                                                                                                          | Benefits                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pattern generator loop macros                                                                                                                                                                     | Provide continuous DigRF v3 stimulus to replace a missing DigRF v3-based BB-IC or RF-IC<br>Run at any DigRF v3-compliant operating mode (sleep, low power or high speed) with<br>performance headroom                                                                                                                            |  |  |  |  |

| Maximum stimulus speed: 312 Mbps                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Stimulus Voltage Level compliant<br>with standard                                                                                                                                                 | Generate DigRF v3 traffic, no matter which DigRF v3-compliant voltage level you are using                                                                                                                                                                                                                                        |  |  |  |  |

| SysClk speed support: 26.0 MHz                                                                                                                                                                    | Generate DigRF v3 traffic, no matter which DigRF v3-compliant speed you are using.                                                                                                                                                                                                                                               |  |  |  |  |

| Connect to target via SMA connectors                                                                                                                                                              | Provide stimulus to compensate for a missing BB-IC or RF-IC                                                                                                                                                                                                                                                                      |  |  |  |  |

| Modify critical control settings while<br>looping (e.g. adjust RF-IC amplifier gain)                                                                                                              | See how your device or system responds without stopping the stimulus probe to change control settings                                                                                                                                                                                                                            |  |  |  |  |

| Create digital control and data stimulus<br>in a simple ASCII format using Signal<br>Studio, Advanced Design System (ADS),<br>a captured logic analyzer trace, or a<br>custom programming package | Use your tool of choice to generate your stimulus data                                                                                                                                                                                                                                                                           |  |  |  |  |

| Convert raw IQ ASCII data and<br>user-defined control information to<br>DigRF v3-compliant data and control<br>packets                                                                            | Automation saves time and eliminate errors                                                                                                                                                                                                                                                                                       |  |  |  |  |

| User specification of order and timing of control and data packets.                                                                                                                               | Evaluate the DUT under a variety of control configurations, data patterns, and timing sequences. NOTE: Stimulus order and timing of control and data packets is determined when the N4860A is set up. Order and timing of data and control packets is NOT altered in response to the "Clear To Send" when stimulating the RF-IC. |  |  |  |  |

### N4850A and N4860A Physical Characteristics

Dimensions

Figure 18. N4850A exterior dimensions

### N4850A and N4860A Physical Characteristics (continued)

Figure 20. N4860A exterior dimensions

Figure 21. N4860A front panel, rear panel, and top view

| Power                                            |                                              |

|--------------------------------------------------|----------------------------------------------|

| 12 V and 5 A (60 W) max                          |                                              |

| Weight                                           |                                              |

| Max net                                          | 2.0 kg (4.4 lbs)                             |

| Max shipping                                     | 4.5 kg (10.0 lbs)                            |

| DataSheet4U.com<br>Instrument operating environm | ent                                          |

| Temperature                                      | 0 °C to 55 °C ( 32 °F to 131 °F)             |

| Altitude                                         | To 3000 m (10,000 ft)                        |

| Humidity                                         | 8 to 80% relative humidity at 40 °C (104 °F) |

### **Ordering Information**

When you configure your DigRF v3 measurement system,consider the following:

1. Ability to provide DigRF v3

**stimulus:** For comprehensive stimulus and response testing of your DigRF v3 device or system, select a logic analyzer with digital pattern generation capability (16822A, 16823A, or a 16900 modular logic analysis system with a 16720A pattern generator module).

- 2. Flexibility to grow as your measurement needs evolve: A modular 16900 Series logic analyzer addresses your measurement needs today and allows you to grow as your needs evolve.

- 3. Modification of the logic analyzer's DigRF v3 protocol decoder: The DigRF v3 standard provides the flexibility to customize your control structure and data packets for your specific application. With the B4641A protocol development kit, you can modify the logic analyer's DigRF v3 protocol decoder to track your custom solution.

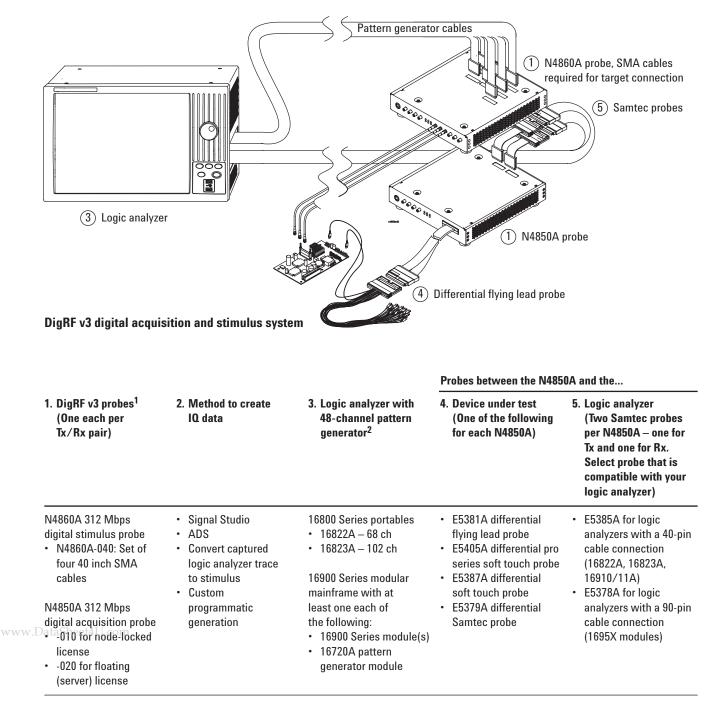

#### Target design and test equipment requirements for DigRF v3 digital acquisition and stimulus measurements

In addition to compatible measurement equipment, the device under test (DUT) requires the following to ensure proper acquisition and stimulus of the DUT.

# DUT requirements for the N4850A acquisition probe:

- Access to SysClk to determine when data is valid on the serial bus

- Probing connection for the acquisition probe, preferably at the receiver. Please refer to the N4850A User Guide and the Agilent N4850A Design Guide (N4850-97002) for information on designing a connection with good signal integrity.

# DUT requirements for use with N4860A stimulus probe:

- SMA (m-m) connectors on the target. The number of SMA connectors depends on your test scenario: BB-IC turn on, RF-IC validation, or system integration

- Place a 50-ohm termination resistor between the positive and negative differential pair

### **Ordering Information** (continued)

To configure a complete DigRF v3 digital acquisition and stimulus system, you will need to order or have the following items:

1 N4860A digital stimulus probe requires an N4850A digital acquisition probe to operate

2 Compatible with 16800 or 16900 Series logic analyzers with 68 channels or more. Diversity mode requires use of a 16900 modular system with one 68-channel (or more) logic analyzer module for each Tx/Rx pair.

### **Ordering Information** (continued)

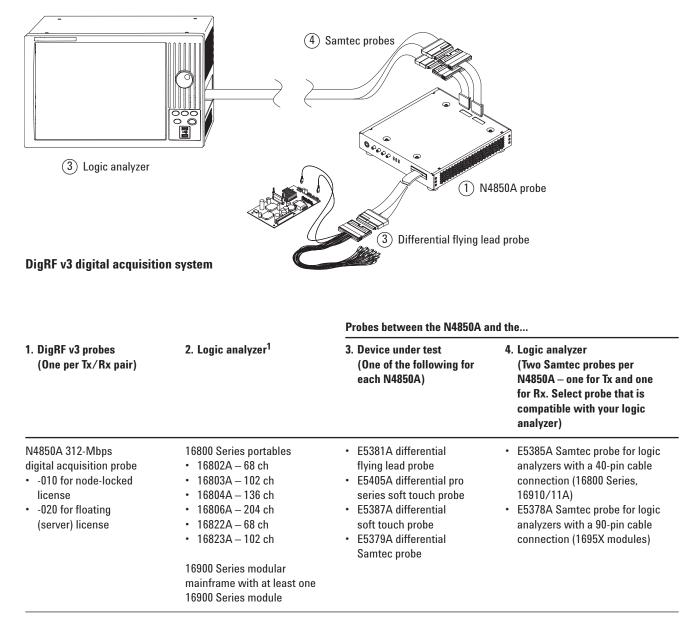

To configure a complete DigRF v3 digital acquisition system, you will need to order or have the following items:

1 Compatible with 16800 or 16900 Series logic analyzers with 68 channels or more www.DataSheet4U.com

### 🔁 Agilent Email Updates

www.agilent.com/find/emailupdates Get the latest information on the products

and applications you select.

#### Agilent Direct

#### www.agilent.com/find/agilentdirect

Quickly choose and use your test equipment solutions with confidence.

#### www.agilent.com/find/open

Agilent Open simplifies the process of connecting and programming test systems to help engineers design, validate and manufacture electronic products. Agilent offers open connectivity for a broad range of system-ready instruments, open industry software, PC-standard I/O and global support, which are combined to more easily integrate test system development.

### LXI

#### www.lxistandard.org

LXI is the LAN-based successor to GPIB, providing faster, more efficient connectivity. Agilent is a founding member of the LXI consortium.

#### **Related literature**

| Publication title                                             | Publication type | Publication number |

|---------------------------------------------------------------|------------------|--------------------|

| Agilent 16800 Series Portable Logic Analyzers                 | Data sheet       | 5989-5063EN        |

| Agilent 16900 Series Logic Analysis Mainframes                | Data sheet       | 5989-0421EN        |

| Probing Solutions for Agilent Technologies<br>Logic Analyzers | Catalog          | 5968-4632E         |

#### **Product Web site**

For the most up-to-date and complete application and product information, please visit our product Web site at: www.agilent.com/find/DigRF

#### www.agilent.com/find/DigRF

Agilent Technologies

For more information on Agilent Technologies' products, applications or services, please contact your local Agilent office. The complete list is available at:

#### www.agilent.com/find/contactus

#### Americas

**Remove all doubt**

Our repair and calibration services

will get your equipment back to you,

performing like new, when promised.

You will get full value out of your Agilent

equipment throughout its lifetime. Your

equipment will be serviced by Agilenttrained technicians using the latest

factory calibration procedures, automated

repair diagnostics and genuine parts. You

will always have the utmost confidence

Agilent offers a wide range of additional

expert test and measurement services

for your equipment, including initial

start-up assistance, onsite education

and training, as well as design, system

For more information on repair and

www.agilent.com/find/removealldoubt

integration, and project management.

calibration services, go to:

in your measurements.

| (877) 894-4414                   |

|----------------------------------|

| 305 269 7500                     |

| (800) 829-4444                   |

|                                  |

| 1 800 629 485                    |

| 800 810 0189                     |

| 800 938 693                      |

| 1 800 112 929                    |

| 0120 (421) 345                   |

| 080 769 0800                     |

| 1 800 888 848                    |

| 1 800 375 8100                   |

| 0800 047 866                     |

| 1 800 226 008                    |

| ast                              |

| 0820 87 44 11                    |

| 32 (0) 2 404 93 40               |

| 45 70 13 15 15                   |

| 358 (0) 10 855 2100              |

| 0825 010 700*                    |

| *0.125 $\in$ fixed network rates |

| 01805 24 6333**                  |

| **0.14 €/minute                  |

| 1890 924 204                     |

| 972-3-9288-504/544               |

| 39 02 92 60 8484                 |

| 31 (0) 20 547 2111               |

| 34 (91) 631 3300                 |

| 0200-88 22 55                    |

| (French)                         |

| 44 (21) 8113811 (Opt 2)          |

| (German)                         |

| 0800 80 53 53 (Opt 1)            |

| 44 (0) 118 9276201               |

| untries:                         |

| 'find/contactus                  |

|                                  |

|                                  |

Product specifications and descriptions in this document subject to change without notice.

© Agilent Technologies, Inc. 2007 Printed in USA, December 6, 2007 5989-6058EN